Con la conferenza annuale Hot Chips che si svolge questa settimana, molte delle più grandi aziende di progettazione di chip del settore sono presenti alla fiera per parlare dei loro prodotti più recenti e/o futuri. Per Intel si tratta di quest’ultimo caso: l’azienda è presente a Hot Chips per parlare della prossima generazione di processori Xeon, Granite Rapids e Sierra Forest, il cui lancio è previsto per il 2024. Intel ha già rivelato questi processori nella sua roadmap per i data center, aggiornandola di recente a marzo di quest’anno, e per Hot Chips l’azienda sta offrendo un po’ più di dettagli tecnici sui chip e sulla loro piattaforma condivisa.

Sebbene non esista una generazione “poco importante” per i processori Xeon di Intel, Granite Rapids e Sierra Forest promettono di essere uno dei più importanti aggiornamenti di Intel all’ecosistema hardware Xeon Scalable, grazie all’introduzione degli E-cores ad alta efficienza di area. Già presenti nei processori consumer di Intel a partire dalla 12a generazione di Core (Alder Lake), con l’imminente piattaforma Xeon Scalable di prossima generazione gli E-cores verranno finalmente portati sulla piattaforma server di Intel. Tuttavia, a differenza dei componenti consumer in cui entrambi i tipi di core sono mescolati in un singolo chip, Intel sta optando per una strategia puramente omogenea, offrendoci il Granite Rapids, interamente P-core, e il Sierra Forest, interamente E-core.

Essendo il primo chip Xeon Scalable E-core di Intel per i data center, Sierra Forest è probabilmente il più importante dei due chip. È il veicolo principale di Intel per il nodo di processo Intel 3 basato su EUV ed è il primo Xeon a uscire. Secondo l’azienda, il lancio è previsto per il primo semestre del 2024. Nel frattempo, Granite Rapids arriverà “a breve” dietro di lui, sullo stesso nodo di processo Intel 3.

Dal momento che Intel ha in programma di fornire due Xeon piuttosto diversi in un’unica generazione, un elemento importante della piattaforma Xeon Scalable di prossima generazione è che entrambi i processori condivideranno la stessa piattaforma. Ciò significa lo stesso socket, la stessa memoria, la stessa filosofia di progettazione basata su chiplet, lo stesso firmware, ecc. Anche se ci sono ancora differenze, in particolare per quanto riguarda il supporto AVX-512, Intel sta cercando di rendere questi chip il più intercambiabili possibile.

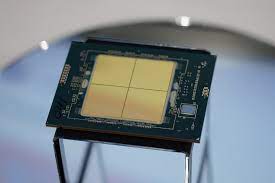

Come annunciato da Intel nel 2022, sia Granite che Sierra sono progetti basati su chiplet, che si basano su un mix di chiplet di calcolo e di I/O uniti insieme grazie alla tecnologia EMIB bridge attiva di Intel. Sebbene non si tratti del primo ballo di Intel con i chiplet nello spazio Xeon (l’onore spetta all’XCC Sapphire Rapids), si tratta di un’evoluzione distinta del design dei chiplet, che utilizza chiplet di calcolo/IO distinti invece di ricucire insieme chiplet Xeon altrimenti “completi”. Tra l’altro, questo significa che Granite e Sierra possono condividere il chiplet I/O comune (costruito sul processo Intel 7) e, dal punto di vista della produzione, il fatto che uno Xeon sia Granite o Sierra è “solo” una questione di quale tipo di chiplet di calcolo viene collocato.

In particolare, Intel conferma per la prima volta che la piattaforma Xeon Scalable di prossima generazione è dotata di funzionalità di auto-avvio, il che la rende un vero SoC. Poiché Intel ha inserito tutte le funzioni di I/O necessarie per il funzionamento all’interno dei chiplet di I/O, non è necessario un chipset esterno (o una FPGA) per far funzionare questi processori. In questo modo la linea Xeon di Intel si avvicina in termini di funzionalità alla linea EPYC di AMD, che da qualche tempo si autoavvia in modo simile.

Complessivamente, la piattaforma Xeon Scalable di prossima generazione supporterà fino a 12 canali di memoria, scalando con il numero e le capacità dei compute dies presenti. Come rivelato in precedenza da Intel, questa piattaforma sarà la prima a supportare la nuova DIMM Multiplexer Combined Ranks (MCR), che essenzialmente raggruppa due gruppi/rami di chip di memoria per raddoppiare la larghezza di banda effettiva da e verso la DIMM. Grazie alla combinazione di velocità di bus di memoria più elevate e di un maggior numero di canali di memoria, Intel afferma che la piattaforma è in grado di offrire un’ampiezza di banda 2,8 volte superiore a quella degli attuali Xeon Sapphire Rapids.

Per quanto riguarda l’I/O, uno Xeon con configurazione massima sarà in grado di offrire fino a 136 corsie di I/O generale, nonché fino a 6 collegamenti UPI (144 corsie in totale) per la connettività multi-socket. Per quanto riguarda l’I/O, la piattaforma supporta il PCIe 5.0 (perché non c’è il PCIe 6.0? Ci è stato detto che la tempistica non ha funzionato), così come il più recente standard CXL 2.0. Come avviene tradizionalmente per gli Xeon big-core di Intel, i chip Granite Rapids saranno in grado di scalare fino a 8 socket in totale. Sierra Forest, invece, sarà in grado di scalare solo fino a 2 socket, a causa del numero di core della CPU in gioco e dei diversi casi d’uso che Intel si aspetta dai suoi clienti.

Oltre ai dettagli sulla piattaforma condivisa, Intel offre per la prima volta anche una panoramica di alto livello delle architetture utilizzate per gli E-cores e i P-cores. Come avviene ormai da molte generazioni di Xeon, Intel sfrutta la stessa architettura di base delle CPU che vengono utilizzate per i prodotti consumer. Quindi Granite e Sierra possono essere considerati come processori Meteor Lake decostruiti, con Granite che riceve i P-cores Redwood Cove e Sierra che riceve gli E-cores Crestmont.

Come già detto, questa è la prima incursione di Intel nell’offerta di core E per il mercato Xeon. Per Intel, ciò ha significato mettere a punto il proprio design E-core per i carichi di lavoro dei data center, in contrapposizione ai carichi di lavoro incentrati sui consumatori che definivano il design E-core della precedente generazione.

Anche se non si tratta di un approfondimento sull’architettura in sé, Intel ha rivelato che Crestmont offre un percorso di decodifica delle istruzioni a 6 larghezze e un backend di pensionamento a 8 larghezze. Sebbene non sia così potente come i core P di Intel, l’E-core non è affatto un core leggero e le decisioni di progettazione di Intel riflettono questo aspetto. Tuttavia, è stato progettato per essere molto più efficiente sia in termini di spazio nello stampo che di consumo energetico rispetto ai core P che entreranno in Granite.

La cache delle istruzioni L1 (I-cache) di Crestmont sarà di 64 KB, la stessa dimensione di Gracemont. Nel frattempo, la novità della linea E-core con Crestmont è che i core possono essere confezionati in cluster da 2 o 4 core, a differenza dell’attuale Gracemont, che è disponibile solo come cluster da 4 core. Questo è essenzialmente il modo in cui Intel regolerà il rapporto tra la cache L2 e i core della CPU; con 4 MB di L2 condivisa indipendentemente dalla configurazione, un cluster a 2 core offre a ciascun core il doppio di L2 per core rispetto a quello che avrebbe altrimenti. In questo modo Intel dispone di un’altra manopola per regolare le prestazioni del chip; i clienti che necessitano di un design Sierra leggermente più performante (piuttosto che massimizzare il numero di core della CPU) possono invece ottenere meno core con le prestazioni più elevate derivanti da una cache L2 effettivamente più grande.

Infine, per quanto riguarda Sierra/Crestmont, il chip offrirà una parità di istruzioni il più possibile simile a quella di Granite Rapids. Ciò significa il supporto del tipo di dati BF16 e di vari set di istruzioni come AVX-IFMA e AVX-DOT-PROD-INT8. L’unica cosa che non troverete qui, oltre a un motore di matrice AMX, è il supporto per AVX-512; il formato vettoriale ultra-largo di Intel non fa parte del set di funzionalità di Crestmont. In ultima analisi, AVX10 contribuirà a risolvere questo problema, ma per il momento questo è il massimo che Intel può ottenere per la parità tra i due processori.

Nel frattempo, per Granite Rapids abbiamo il P-core Redwood Cove. Cuore tradizionale di un processore Xeon, Redwood/Granite non sono un grande cambiamento per Intel come lo è Sierra Forest. Ma questo non significa che se ne stiano con le mani in mano.

In termini di microarchitettura, Redwood Cove ha la stessa I-cache da 64 KB che abbiamo visto su Crestmont e che, a differenza dei core E, ha una capacità doppia rispetto al suo predecessore. È raro che Intel tocchi la capacità della I-cache (a causa del bilanciamento tra hit rate e latenza), quindi questo è un cambiamento notevole e sarà interessante vedere le ramificazioni quando Intel parlerà di più dell’architettura.

Ma soprattutto, Intel è riuscita a ridurre ulteriormente la latenza della moltiplicazione in virgola mobile, portandola da 4/5 cicli a soli 3 cicli. Miglioramenti della latenza delle istruzioni fondamentali come questi sono rari, quindi sono sempre benvenuti.

Per il resto, i punti salienti della microarchitettura Redwood Cove sono la predizione delle ramificazioni e il prefetching, che sono obiettivi di ottimizzazione tipici di Intel. Tutto ciò che si può fare per migliorare la predizione delle ramificazioni (e ridurre il costo delle rare mancanze) tende a pagare dividendi relativamente grandi in termini di prestazioni.

Per quanto riguarda la famiglia Xeon in particolare, il motore di matrici AMX per Redwood Cove sta ottenendo il supporto per FP16. FP16 non è così pesantemente utilizzato come BF16 e INT8 già supportati, ma è un miglioramento della flessibilità generale di AMX.

Anche il supporto alla crittografia della memoria è stato migliorato. La versione di Redwood Cove di Granite Rapids supporterà 2048 chiavi di memoria a 256 bit, rispetto alle 128 di Sapphire Rapids. Anche le funzionalità Cache Allocation Technology (CAT) e Code and Data Prioritization (CDP) sono state migliorate e Intel le ha estese in modo da poter controllare ciò che viene inserito nella cache L2, anziché solo nella cache LLC/L3 come nelle precedenti implementazioni.

In definitiva, è ovvio che Intel ritiene di essere ben posizionata per il 2024 e oltre con i suoi prossimi Xeon. Migliorando le prestazioni degli Xeon P-core di fascia alta e introducendo al contempo gli Xeon E-core per i clienti che hanno bisogno di molti core di CPU più leggeri, Intel ritiene di poter affrontare l’intero mercato con due tipi di CPU che condividono un’unica piattaforma comune.

Sebbene sia ancora troppo presto per parlare di singole SKU per Granite Rapids e Sierra Forest, Intel ci ha detto che il numero di core in generale sta aumentando. I componenti Granite Rapids offriranno più core di CPU rispetto a Sapphire Rapids (da 60 per SPR XCC) e, naturalmente, con 144 core Sierra offrirà ancora di più. Tuttavia, Intel non segmenterà le due linee di CPU in base al numero di core: Sierra Forest sarà disponibile anche con un numero di core inferiore (a differenza dei chip EPYC Zen4c Bergamo di AMD). Questo riflette le diverse capacità prestazionali dei core P ed E e, senza dubbio, la volontà di Intel di sfruttare appieno la scalabilità derivante dall’uso dei chiplet.

Mentre Sierra Forest arriverà già a 144 core di CPU, Intel ha anche fatto un commento interessante durante il nostro pre-briefing: avrebbe potuto aumentare il numero di core per il suo primo processore E-core Xeon Scalable. Ma l’azienda ha deciso di dare maggiore priorità alle prestazioni per core, ottenendo così i chip e il numero di core che vedremo l’anno prossimo.

Soprattutto – e forse lasciando che il marketing prenda il timone un po’ troppo a lungo per Hot Chips – Intel sta insistendo sul fatto che i processori Xeon di prossima generazione sono ancora in linea con il lancio previsto per il 2024. Va da sé che Intel si sta appena riprendendo dagli enormi ritardi di Sapphire Rapids (e dall’effetto a catena su Emerald Rapids), quindi l’azienda vuole assicurare ai clienti che Granite Rapids e Sierra Forest sono i momenti in cui Intel si rimette in carreggiata. Tra i precedenti ritardi di Xeon e il tempo necessario per immettere sul mercato un chip E-core Xeon Scalable, Intel non ha più dominato il mercato dei data center come un tempo, quindi Granite Rapids e Sierra Forest segneranno un importante punto di inflessione per le offerte di Intel per i data center in futuro.